- Jobs

- Entreprises

-

Accès recruteur

-

Emploi

- Formation

-

Mon compte

-

Stage Ingenieur Algorithme pour l'IA Embarquée Via Hw-Nas H/F ELSYS Design

- Cachan - 94

- Stage

- Bac +5

- Secteur informatique • ESN

Détail du poste

L'Edge-AI regroupe l'ensemble des méthodes, outils, technologies, qui permettent la mise en place d'algorithmes d'Intelligence Artificielle (IA) directement sur le terrain (« at the edge »), au plus près de l'utilisateur final [1]. Son utilisation dans des domaines comme la surveillance de patients ou la création d'implants intelligents dans le domaine médical, la maintenance prédictive pour l'industrie 4.0 ou l'automobile, ou toute application basée sur de l'acquisition et du traitement de données, promet une réduction des temps de latence, de la bande passante utilisée, de l'énergie consommée, et donc de la pertinence des décisions prises en conséquence [2].

La conception de solutions industrielles dans ce domaine fait face à un certain nombre de contraintes. Tout d'abord, les dispositifs embarqués disposent de ressources limitées en mémoire et en puissance de calcul. Leur consommation énergétique, notamment dans le cas d'appareils sur batterie, possède un budget fortement limité. Enfin, l'hétérogénéité des architectures de calculateurs disponibles (MCU avec NPU/TPU, FPGA avec accélérateur spécifique, processeur neuromorphique, etc.) complexifie la conciliation logicielle et matérielle permettant le déploiement efficace, frugal et explicable d'algorithmes d'IA. La création d'applications adaptées au matériel requiert donc actuellement une expertise large avec des temps de conception et développements conséquents, incompatibles avec un marché en évolution très rapide avec des besoins immédiats.

Les algorithmes NAS (Neural Architecture Search) permettent d'explorer automatiquement un espace de solutions donné en vue de constituer un réseau de neurone artificiel (ANN, Artificial Neural Network) optimisé par rapport à une fonction de coût [3]. En particulier, les variantes HW-NAS (HW pour Hardware) visent à intégrer les contraintes matérielles (nombre d'opérations par seconde en FLOPS, latences mémoires, etc.) dans les fonctions de coût utilisées afin de créer des architectures de modèles qui ne nécessiteront pas d'être fortement dégradé pour fonctionner sur la cible d'exécution. Cependant, ces approchent ne considèrent pas actuellement à notre connaissance les transformations ultérieures (scheduling, appel à un runtime particulier, optimisations de code appliquées, etc.) permettant de déployer un graphe de calcul sur une architecture matérielle et logicielle donnée.

Ce stage vise à explorer de nouvelles utilisations des représentations intermédiaires MLIR (Multi Level Intermediate Representation [4]) en vue de développer de nouveaux algorithmes HW-NAS pour la création de modèles d'IA embarqué frugaux et explicables. En particulier, un exemple de maintenance prédictive appliqué à des moteurs de drones servira de cas d'application. Les objectifs de ce stage sont :

De mettre en oeuvre une chaîne de compilation pour IA embarquée basée sur ONNX, les représentations MLIR, Polygeist (compilation C vers MLIR), et clang pour la compilation.

De porter, en utilisant cette chaîne de compilation, un modèle LSTM/SRU développé lors d'un stage précédent.

D'implémenter, si besoin, des passes de transformation de la représentation MLIR en utilisant LLVM ou la bibliothèque python xDSL ;

Instrumenter un banc de test permettant l'évaluation de l'exécution du modèle sur la cible (banc de test Hardware-In-The-Loop, ou HIL) ;

Mettre en oeuvre plusieurs méthodes HW-NAS identifiées dans la littérature scientifique (simple, multi-agents) dans le but d'en faire une évaluation comparative ;

Comparer les résultats de ces approches avec l'utilisation du modèle LSTM/SRU ;

Proposer une nouvelle approche prenant en compte les spécificités liées à la transformation du graphe de calcul du modèle en binaire déployable sur la cible d'exécution.

En particulier, les contributions effectuées dans le cadre de ce stage pourront donner lieu :

A une intégration au sein du projet OVERITY-AI, avec une release open-source à terme ;

A la rédaction d'un papier scientifique en vue de le présenter en conférence ou l'intégrer à une revue, selon la conséquence du travail abordé.

Le coeur du stage se situe sur la maîtrise de la chaîne de valeur permettant de partir d'une représentation abstraite d'un modèle d'IA, pour aller jusqu'à son exécution sur une cible embarquée, avec le haut niveau d'exigence, de traçabilité et de contraintes techniques demandés par le métier. Il s'agit d'aller plus loin que l'existant, développer une expertise sur les nouvelles technologies du marché permettant ce type d'application.

Environnement technique

L'environnement technique sera essentiellement constitué des éléments suivants :

Environnement de développement Windows/Linux ;

Banc de test linux ;

Frameworks AI/ML : PyTorch ;

Toolchain de compilation basée sur LLVM : Clang/polygeist et outils MLIR ;

xDSL pour l'implémentation de certaines transformations manuelles ;

Développement embarqué en C/Rust ;

Utilisation du framework overity.ai développé en interne pour la traçabilité des développements effectués.

Compétences acquises

Les compétences acquises seront principalement :

Maîtrise d'un système complet (HW/SW) ;

Prise en main d'une chaîne complète de développement d'un système embarqué (compilation logicielle, outillage d'un banc de test, etc.) ;

Découverte du fonctionnement et du processus d'intégration de fonctions intelligentes au sein d'une plateforme embarquée.

Contribuer à l'innovation scientifique au travers d'un état de l'art, l'identification d'un verrou scientifique, et l'apport d'une réponse innovante et justifiée pouvant donner lieu à une publication dans un journal.

L'agence de rattachement de cette offre se situe à Paris.

Profil Recherché

Vous êtes en 3ème année de cycle ingénieur, et visez une spécialisation dans les systèmes embarqués, avec une majeure sur la partie logicielle. Vous avez des compétences solides en python, développement C embarqué, des notions d'électronique sur le choix des composants, éventuellement quelques connaissances de base sur le codage matériel en VHDL et/ou Verilog.

Autonomie, enthousiasme pour les nouvelles technologies, rigueur et travail en équipe sont des qualités essentielles.

Votre implication sur des projets extrascolaires de conception (Coupe de France de Robotique, fab labs, projets personnels, junior entreprise, etc.), est un plus qui sera apprécié.

Ce stage est conventionné et rémunéré.

La mission peut être réalisée dans le cadre d'une année de césure ou d'un stage de fin d'études.

Lieu : Cachan

Avantages Salariaux

-

- Titre restaurant presque intégralement pris en charge

-

- Accès aux activités sociales et culturelles du CSE

- Remboursement de 70% du Pass Navigo en Île-de-France

Qui sommes-nous

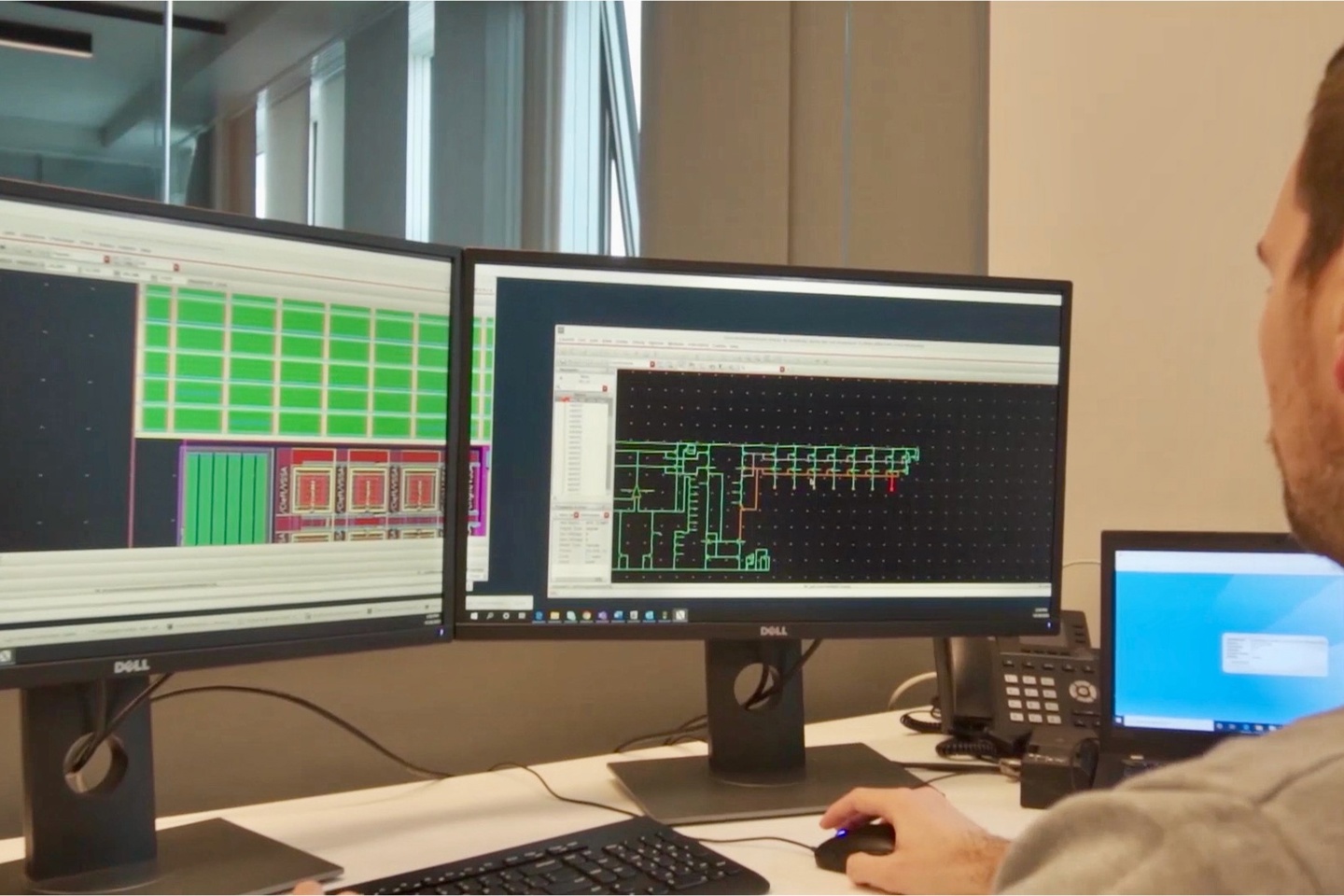

ELSYS Design est une société d'ingénierie spécialisée dans la conception de systèmes électroniques embarqués.

Nous accompagnons nos clients issus de secteurs variés (énergie, semiconducteur, défense, spatial, transport, etc.) dans 4 domaines principaux : la microélectronique (FPGA, ASIC, SoC), la carte, le logiciel embarqué et l'ingénierie système.

Chez ELSYS Design, nous sommes tous ingénieurs, votre manager sera donc lui aussi issu de la technique. Il veillera à vous proposer des projets pertinents qui vous permettront de vous constituer une expérience riche, bâtie sur un socle de compétences recherchées.

Vous aimez relever des défis techniques ? Vous avez envie d'évoluer dans une ambiance humaine, bienveillante et responsabilisante ? D'intégrer une structure familiale, présentant les avantages d'un grand groupe ?

Alors, n'hésitez plus : postulez et rencontrons-nous !

0 - 65 000 Eur (€)

Nos étapes de recrutement

Les étapes de recrutement peuvent varier selon l’offre à laquelle vous postulez.

-

1er entretien avec le responsable d’affaires en charge de l’activité

-

2ème entretien technique avec le référent métier pour qualifier vos compétences techniques

-

3ème rendez-vous avec le responsable de centre ou le directeur régional

Raisons de nous rejoindre

-

Accords de participation et d'intéressement

-

Carte Swile pour les tickets restaurants

-

Des événements tout au long de l'année, dont un séminaire annuel

-

Prime de cooptation

-

Prime vacances

-

Un CSE très actif

-

Horaires de travail flexibles

-

Frais de transport

Localiser le poste

Pas de salaire renseigné

Publiée le 09/10/2025 - Réf : E-C-20251009-143901

Stage Ingenieur Algorithme pour l'IA Embarquée Via Hw-Nas H/F

- Cachan - 94

- Stage

Pour les postes éligibles :

Télétravail partielCréez une alerte

Pour être informé rapidement des nouvelles offres, merci de préciser les critères :

Envoyez votre candidature

dès maintenant !

Créez votre compte et

envoyez votre candidature !

dès maintenant !

envoyez votre candidature !

Ces offres pourraient aussi

vous intéresser

Recherches similaires

- Offre emploi Ingénieur

- Offre emploi Logistique

- Offre emploi Rungis

- Offre emploi Villiers-sur-Marne

- Offre emploi Créteil

- Offre emploi Orly

- Offre emploi Ivry-sur-Seine

- Offre emploi Vincennes

- Offre emploi Vitry-sur-Seine

- Offre emploi Sucy-en-Brie

- Offre emploi Nogent-sur-Marne

- Offre emploi Champigny-sur-Marne

- Offre emploi Cariste

- Offre emploi Préparateur de commande

- Offre emploi Manutentionnaire

- Offre emploi Magasinier

- Offre emploi Agent de quai

- Entreprises Logistique

- Stage Logistique

- Entreprises Ingénieur

- Entreprises Cachan

- Stage Val-de-Marne

- Stage Cachan

- Stage Ingénieur

- Stage Ingénieur Cachan

- Offre emploi Etat

- Offre emploi Logiciel

- Offre emploi Rapide

- Offre emploi Scientifique

- Offre emploi Technologies

- Offre emploi Cycle Cachan

- Offre emploi Cse Cachan

- Offre emploi Robotique Cachan

{{title}}

{{message}}

{{linkLabel}}