- Jobs

- Entreprises

-

Accès recruteur

-

Emploi

- Formation

-

Mon compte

-

Stage R&D Architecture d'Intégration d'IP sur Fpga pour Système Iot H/F ELSYS Design

- Cachan - 94

- Stage

- Bac +5

- Secteur informatique • ESN

Détail du poste

Les FPGAs (Field Programmable Gate Arrays) occupent aujourd'hui une place centrale, depuis les systèmes embarqués et SoCs jusqu'aux infrastructures cloud. Ils offrent une combinaison rare de performance, efficacité énergétique et reprogrammabilité, qui en fait des plateformes idéales de prototypage rapide et d'intégration. Cependant, ce potentiel est fortement limité par une difficulté persistante : l'intégration matérielle et logicielle des périphériques développés pour ces plateformes.

Historiquement, l'interaction processeur-périphérique repose sur des registres matériels exposés comme des accès mémoire. Cette approche, héritée des années 60, pose aujourd'hui des limites : exposition excessive de détails bas-niveau (>1000 registres pour certains devices) [1], complexité croissante pour la documentation et la virtualisation, et difficultés pour les ingénieurs matériels comme logiciels. On observe aujourd'hui les conséquences de cette complexité dans le monde Linux dans lequel 70% de la base de code est constitué uniquement de driver [2]. Ceci met en lumières deux verrous majeurs : la dépendance du matériel à son support logiciel et, inversement, la difficulté de déployer un nouvel OS sans une base de drivers solide.

Ces limites soulignent la nécessité d'une redéfinition de la frontière entre matériel et logiciel, et d'une réflexion en co-conception. Des initiatives comme USB, PCIe SR-IOV ou RIFFA [3] dans le monde académique ont déjà montré que des architectures basées sur des flux de paquets pouvaient simplifier et standardiser l'intégration. C'est dans ce contexte que s'inscrit ce stage, qui vise à proposer une solution innovante et générique pour l'intégration d'IP FPGA avec une volonté de contribuer à l'état de l'art.

Le stage :

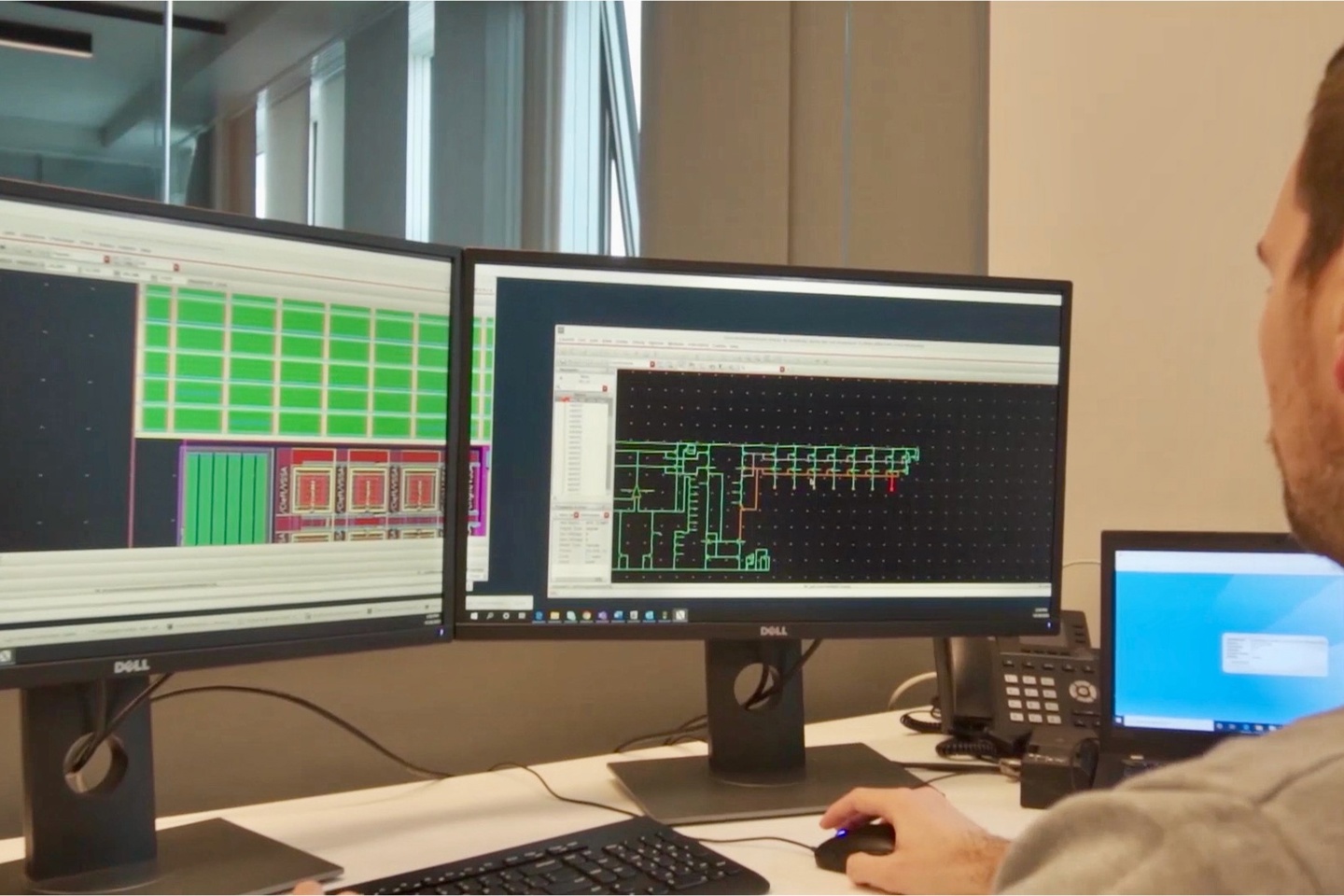

L'objectif est de concevoir et implémenter une solution d'intégration HW/SW basée sur des flux de paquets, couvrant à la fois les briques matérielles et les composants logiciels nécessaires. Côté FPGA, cela inclut des contrôleurs matériels offrant une flexibilité suffisante pour être capable d'intégrer et agréger des technologies de transport diverses tel que SPI, I2C, USB, WiFi, BLE, etc. Côté logiciel, il s'agit de mettre en place un bus logiciel, des drivers et une bibliothèque sur RISC-V, facilitant l'exploitation des IPs pour des applications orientées IoT. La figure ci-dessous montre la nouvelle architecture proposée, consistant à agréger l'ensemble des technologies de transport de l'architecture d'origine (en violet). Cette agrégation consiste en un composant matériel et son driver (en vert) capable de s'interfacer sur les technologies existantes et d'offrir une interface standardisée pour les drivers logiciels.

Le stagiaire sera amené à définir l'architecture, spécifier les protocoles de communication, et développer un premier démonstrateur fonctionnel. Le démonstrateur sera implémenté sur une carte de développement basse consommation iCE40 UltraPlus Breakout Board embarquant un FPGA iCE40 UltraPlus. La plateforme intègrera simultanément un ensemble de capteurs provenant de technologie de transports différentes, démontrant la capacité d'agrégation de la solution.

Tâches prévues :

Revue de littérature scientifique sur le sujet, encadré par le responsable scientifique

Développement FPGA : implémentation des IPs d'adaptation de divers protocoles (SPI, I2C, etc), simulation et validation sur carte

Développement logiciel bas-niveau sur RISC-V : drivers, bibliothèques

Intégration d'un réseau de capteurs IoT communiquant sur un ensemble de protocoles hétérogène

Documentation technique pour assurer la réutilisation de la solution dans les projets futurs

Technologies utilisées :

VHDL / SystemVerilog pour le développement matériel au niveau RTL

C pour le développement logiciel embarqué sur RISC-V

Protocoles pour l'IoT : SPI, I2C, UART, USB

Lattice Propel/Radiant (low-power FPGA)

GitLab & GitLab CI pour le suivi de projet

Compétences acquises :

Conception et développement d'une architecture système matérielle et logicielle

Maîtrise des flux de développement FPGA (design, simulation, intégration sur cible)

Expérience en développement bas niveau (VHDL/SystemVerilog)

Travail en mode projet R&D sur des problématiques d'intégration HW/SW

Capacité à documenter et transférer une solution complexe vers une équipe industrielle

L'agence de rattachement de cette offre se situe à Paris.

Profil Recherché

Tu es en dernière année d'école d'ingénieur avec une spécialisation en systèmes embarqués, électronique numérique ou informatique bas niveau. Tu as déjà des connaissances pratiques en FPGA (VHDL/SystemVerilog) et en développement logiciel en C. Ton autonomie, ta rigueur et ton goût pour l'innovation seront essentiels. Une expérience dans des projets techniques extrascolaires (robotique, fab labs, junior entreprise, etc.) sera un atout apprécié.

Avantages Salariaux

-

-

- Titre restaurant presque intégralement pris en charge

-

- Accès aux activités sociales et culturelles du CSE

-

- Remboursement de 70% du Pass Navigo en Île-de-France

-

Qui sommes-nous

ELSYS Design est une société d'ingénierie spécialisée dans la conception de systèmes électroniques embarqués.

Nous accompagnons nos clients issus de secteurs variés (énergie, semiconducteur, défense, spatial, transport, etc.) dans 4 domaines principaux : la microélectronique (FPGA, ASIC, SoC), la carte, le logiciel embarqué et l'ingénierie système.

Chez ELSYS Design, nous sommes tous ingénieurs, votre manager sera donc lui aussi issu de la technique. Il veillera à vous proposer des projets pertinents qui vous permettront de vous constituer une expérience riche, bâtie sur un socle de compétences recherchées.

Vous aimez relever des défis techniques ? Vous avez envie d'évoluer dans une ambiance humaine, bienveillante et responsabilisante ? D'intégrer une structure familiale, présentant les avantages d'un grand groupe ?

Alors, n'hésitez plus : postulez et rencontrons-nous !

0 - 65 000 Eur (€)

Nos étapes de recrutement

Les étapes de recrutement peuvent varier selon l’offre à laquelle vous postulez.

-

1er entretien avec le responsable d’affaires en charge de l’activité

-

2ème entretien technique avec le référent métier pour qualifier vos compétences techniques

-

3ème rendez-vous avec le responsable de centre ou le directeur régional

Raisons de nous rejoindre

-

Accords de participation et d'intéressement

-

Carte Swile pour les tickets restaurants

-

Des événements tout au long de l'année, dont un séminaire annuel

-

Prime de cooptation

-

Prime vacances

-

Un CSE très actif

-

Horaires de travail flexibles

-

Frais de transport

Localiser le poste

Pas de salaire renseigné

Publiée le 09/10/2025 - Réf : E-C-20251009-144051

Stage R&D Architecture d'Intégration d'IP sur Fpga pour Système Iot H/F

- Cachan - 94

- Stage

Pour les postes éligibles :

Télétravail partielCréez une alerte

Pour être informé rapidement des nouvelles offres, merci de préciser les critères :

Envoyez votre candidature

dès maintenant !

Créez votre compte et

envoyez votre candidature !

dès maintenant !

envoyez votre candidature !

Ces offres pourraient aussi

vous intéresser

Recherches similaires

- Job Ingénieur intégration

- Job Graphisme

- Job Rungis

- Job Créteil

- Job Villiers-sur-Marne

- Job Orly

- Job Ivry-sur-Seine

- Job Vincennes

- Job Vitry-sur-Seine

- Job Sucy-en-Brie

- Job Nogent-sur-Marne

- Job Champigny-sur-Marne

- Job Concepteur

- Job Intégrateur

- Job Graphiste

- Job Infographiste

- Job UX designer

- Entreprises Graphisme

- Offre de stage Graphisme

- Entreprises Ingénieur intégration

- Entreprises Cachan

- Offre de stage Val-de-Marne

- Offre de stage Cachan

- Offre de stage Ingénieur intégration

- Offre de stage Ingénieur intégration Cachan

- Job Iot

- Job Numérique

- Job Etat

- Job Logiciel

- Job Rapide

- Job Cse Cachan

- Job Robotique Cachan

{{title}}

{{message}}

{{linkLabel}}