Détail du poste

ELSYS Design recherche un(e) ingénieur(e) en microélectronique pour intégrer nos équipes et participer au développement d'IPs sur FPGAs et/ou ASICs. Dans ce contexte, vous travaillerez en équipe pour assurer le bon développement des IPs et assurer leurs intégrations Top level , accompagné de notre leader technique.

Vos responsabilités :

- Participer à la définition de l'architecture des IPs

- Implémenter la description RTL de ces blocs.

- Intégrer au niveau top

- Vérifier les modules en Tests Unitaires

- Construire et exécuter les plans de vérification en collaboration avec l'équipe Vérification

- Rédiger la documentation interne et externe

L'agence de rattachement de cette offre se situe à Rennes. L'agence de rattachement de cette offre se situe à Rennes.

Profil Recherché

- Vous détenez un diplôme ingénieur Bac +5 en électronique et justifiez d'au moins une première expérience professionnelle sur FPGA ou ASIC numériques.

- Vous maîtrisez au moins un des langages suivants VHDL, Verilog ou SystemVerilog

- Vous avez déjà travaillé avec des outils de gestion de configuration (GIT ou équivalent) et ticketing (Jira)

- Et surtout, vous savez travailler dans différents contextes et nouer de bonnes relations de travail au sein de votre équipe technique !

Avantages Salariaux

-

-

- 10 jours de RTT par an

-

- Allocation repas ou Titre restaurant presque intégralement pris en charge

-

- Mutuelle Santé Famille

-

- Compte Epargne Temps

-

- Participation et Intéressement

-

- Prime de cooptation de 1000 ou 1500 €

-

- Prime de vacances

-

- Prime Transport de 200 € net par an et 50 € brut mensuel.

-

Qui sommes-nous

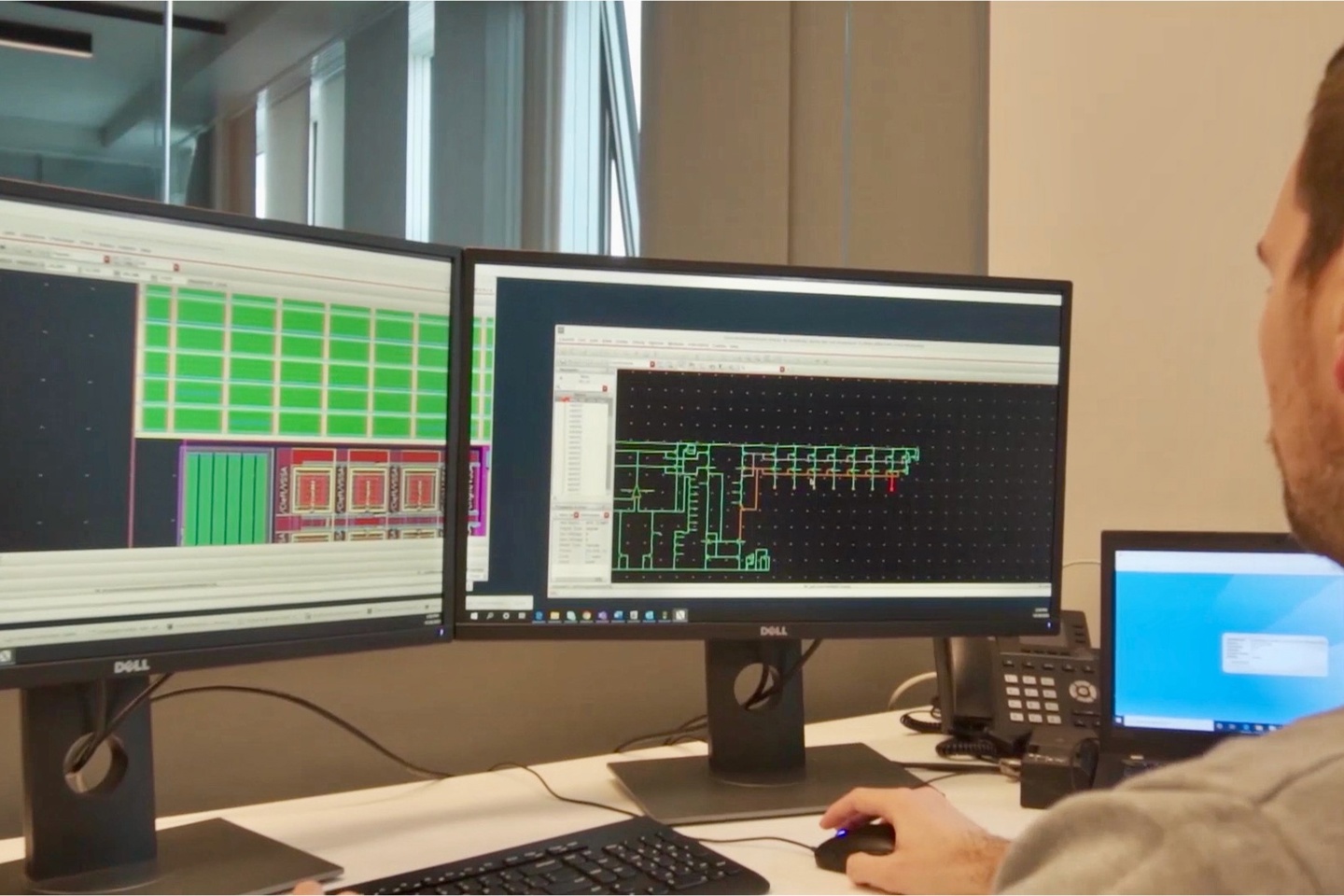

ELSYS Design est une société d'ingénierie spécialisée dans la conception de systèmes électroniques embarqués.

Nous accompagnons nos clients issus de secteurs variés (énergie, semiconducteur, défense, spatial, transport, etc.) dans 4 domaines principaux : la microélectronique (FPGA, ASIC, SoC), la carte, le logiciel embarqué et l'ingénierie système.

Chez ELSYS Design, nous sommes tous ingénieurs, votre manager sera donc lui aussi issu de la technique. Il veillera à vous proposer des projets pertinents qui vous permettront de vous constituer une expérience riche, bâtie sur un socle de compétences recherchées.

Vous aimez relever des défis techniques ? Vous avez envie d'évoluer dans une ambiance humaine, bienveillante et responsabilisante ? D'intégrer une structure familiale, présentant les avantages d'un grand groupe ?

Alors, n'hésitez plus : postulez et rencontrons-nous !

Infos complémentaires

Les étapes de recrutement

Les étapes de recrutement peuvent varier selon l'offre à laquelle vous postulez.

-

1er entretien avec le responsable d’affaires en charge de l’activité

-

2ème entretien technique avec le référent métier pour qualifier vos compétences techniques

-

3ème rendez-vous avec le responsable de centre ou le directeur régional

-

ELSYS Design en images

La carte

7 Square du Chêne Germain

35510 Cesson-Sévigné

Publiée le 11/04/2026 - Réf : E-C-20260311-149414